# **System-level Synthesis**

### **Todor Stefanov**

Leiden Embedded Research Center, Leiden Institute of Advanced Computer Science Leiden University, The Netherlands

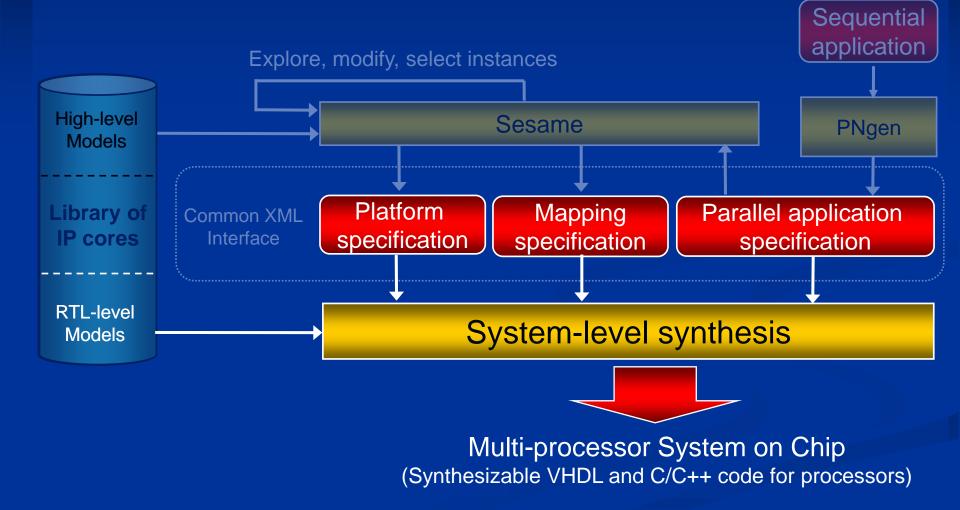

# System-level Synthesis: ESPAM tool

## **ESPAM**

### Embedded System-level Platform Synthesis and Application Mapping

System-Level Simple descriptions in **Platform Spec Mapping Spec** PPN **Specification** XML format in XML in XML in XML Automated System-to-RTL Library of **ESPAM** Level conversion and **IP cores** software code generation C/C++ Ready for direct Platform Auxiliary IP cores code for **RTL-Level** topology files in VHDL implementation processors **Specification** description FPGA-based prototyping Xilinx Platform Studio (XPS) Tool with Xilinx boards Program code Program code Gate-Level Processor 2 Processor 1 All of this in a matter Virtex **Specification FPGA** of hours Program code Processor 3

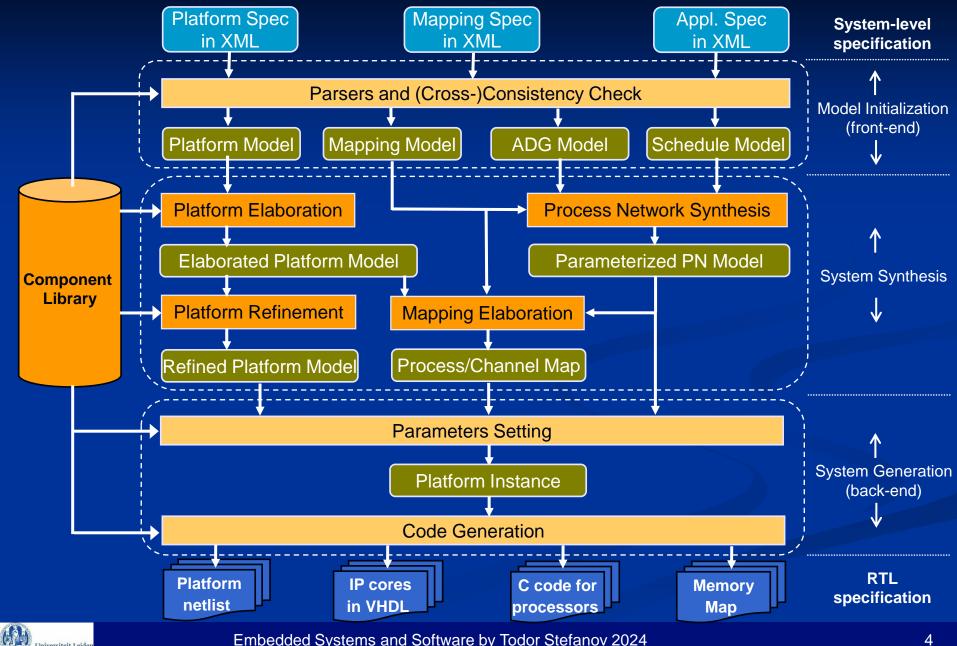

# **ESPAM: Internal Structure**

Embedded Systems and Software by Todor Stefanov 2024

Universiteit Leiden

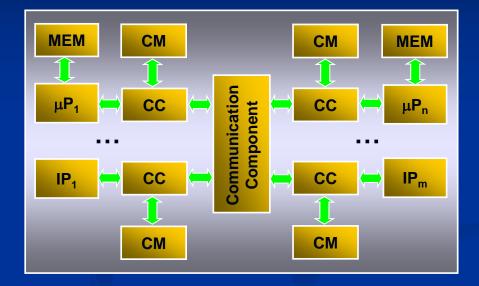

# **MP-SoCs currently considered**

### Library of parameterized components:

- Processing Components:

- Programmable processors

- Hardware IP Cores

- Memory Components:

- Program, Data (on-chip and external) Memory (MEM)

- Communication Memory (CM)

- Communication Components:

- Point-to-point network

- Crossbar switch

- Shared bus with Round-Robin, Fixed Priority, or TDMA arbitration

Many alternative platforms can be constructed fast and easily by instantiating different type/number of components and setting their parameters.

Communication Controller (CC) – interface between processing, memory, and communication components

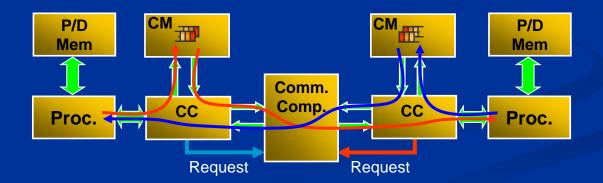

### **Communication and Synchronization**

- Data communication and synchronization between processors only through *FIFOs* mapped in the Communication Memories (CM)

- A processor can write only to its local CM

- A processor can access other CMs only for *read* operations through the communication component using *requests*

- The synchronization mechanism is implemented by *Read* and *Write SW* primitives that interact directly with the *Communication Controllers*

### **Platform Synthesis and Programming**

- Platform Elaboration and Refinement

- Mapping of processes

- FIFOs to CMs mapping

- Memory map of the system

- Program code for each processor

- Read and write synchronization primitives

# **Write and Read Primitives**

#### Write Synchronization Primitive

```

#define writeCM( pos, value, n ) \

```

```

int i;\

volatile int *isFull;\

volatile int *outPort = (volatile int *) pos;\

```

```

isFull = outPort + 1;\

```

```

for (i = 0; i < n; i++) {\

while ( *isFull ) { };\

*outPort = ((volatile int *) value)[ i ];\

}\</pre>

```

#### **Read Synchronization Primitive**

```

#define readCM( pos, value, n ) \

```

```

int i;\

volatile int *isEmpty;\

int inPort = (int) pos;\

(volatile int *) dataReqReg = (volatile int *) 0xE000000;\

```

```

isEmpty = dataReqReg + 1;\

*dataReqReg = 0x80000000 | inPort;\

```

```

for (i = 0; i < n; i++) {\

while ( *isEmpty ) { };\

((volatile int *) value)[ i ] = * dataReqReg;\

}\</pre>

```

\*dataReqReg = 0x7FFFFFF & inPort;\

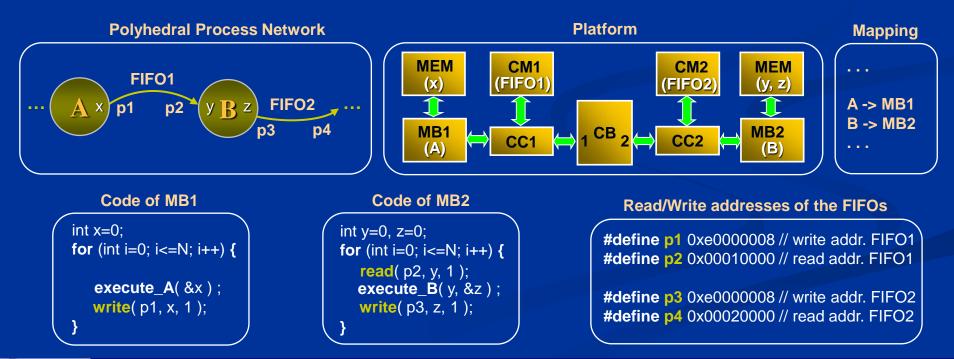

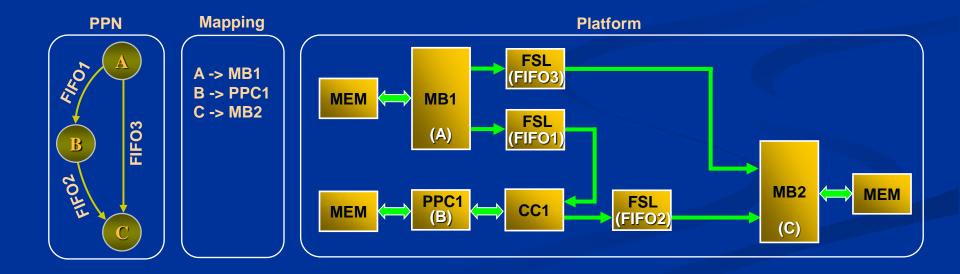

# **Platform Synthesis: Point-to-Point**

No Communication Component, no communication overhead!

- Number of processes in PPN is equal to number of processors in the platform

- Only one process mapped onto one processor

## Write and Read Primitives

#### Write FIFO Synchronization Primitive

```

#define write( pos, value, n ) \

```

```

int i;\

volatile int *isFull;\

volatile int *outPort = (volatile int *) pos;\

```

```

isFull = outPort + 1;\

```

```

for (i = 0; i < n; i++) {\

while ( *isFull ) { };\

*outPort = ((volatile int *) value)[ i ];\

}\</pre>

```

#### Write FSL Synchronization Primitive

```

#define writeFSL( pos, value, n ) \

```

int i;\

#### **Read FIFO Synchronization Primitive**

```

#define read( pos, value, n ) \

```

```

int i;\

volatile int *isEmpty;\

volatile int *inPort = (volatile int *) pos;\

```

```

isEmpty = inPort + 1;\

```

```

for (i = 0; i < n; i++) {\

while ( *isEmpty ) { };\

((volatile int *) value)[ i ] = *inPort;\

}\</pre>

```

#### **Read FSL Synchronization Primitive**

```

#define writeFSL( pos, value, n ) \

```

int i;\

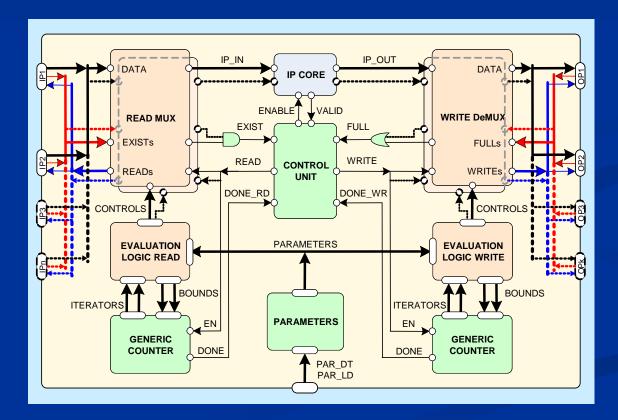

# **Dedicated Hardware IPs Integration with ESPAM**

- To meet higher application requirements,

- integrate hardware IP cores into ESPAM generated systems

- Done by automated HW Module (wrapper) generation

- including/wrapping third-party IP core

- Features of a generated HW module

- modularity, i.e., HW Module consisting of well defined parameterized components

- clearly defined interfaces between components of a HW module

#### Embedded Systems and Software by Todor Stefanov 2024

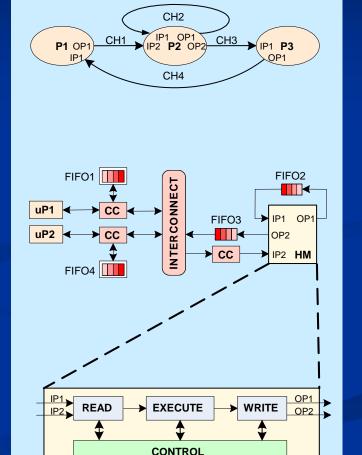

# **PPN to Heterogeneous System**

- Processes mapped to programmable processors and/or dedicated HW IPs

- Hardware Modules wrappers around predefined IP cores

- Read Block

- Execute Block, i.e., the IP core

- Write Block

**Jniversiteit** Leider

Control Block

### HW IPs must provide:

- Function call behavior

- Unidirectional I/O data interfaces

- Enable/Valid control interface

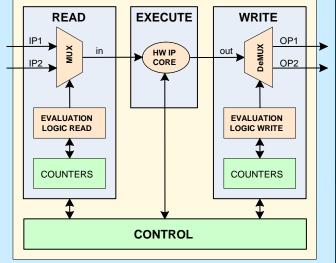

### **Structure of a HW Module**

### Read Block

- Fetch data from communication channels

- For each input argument select from which port to fetch the data using the control information derived from the PPN

### Execute Block

A functional sub-wrapper for the IP core

### Write Block

- Write back the results from the execution to the communication channels

- For each output argument select which port to receive the corresponding data

- Control Block

- Control and synchronize reading, writing and execution

| 1 // process P2<br>2 void main() {                                                                         |         |

|------------------------------------------------------------------------------------------------------------|---------|

| 3 for(int i=2; i<=N; i++)<br>4 for(int j=1; j<=M+i; j++) {                                                 | CONTROL |

| 5                                                                                                          | READ    |

| 9 execute( in_0, out_0);                                                                                   | EXECUTE |

| 10 if(-i+N-1 >= 0)<br>11 write( OP1, out_0, size );<br>12 if( i-N == 0) {<br>13 write( OP2, out_0, size ); | WRITE   |

| 14 } // for j<br>15 } // main                                                                              |         |

# **HW Module Structure in Detail**

Composed of well defined componentsClearly defined component interfaces

### **ESPAM Summary**

### Reduced design time:

Implementations correct by construction

no simulations are needed

Complete implementation and programming

about 2 hours for systems with 5 processors

Design space exploration is feasible at implementation level

100% accuracy

### http://daedalus.liacs.nl